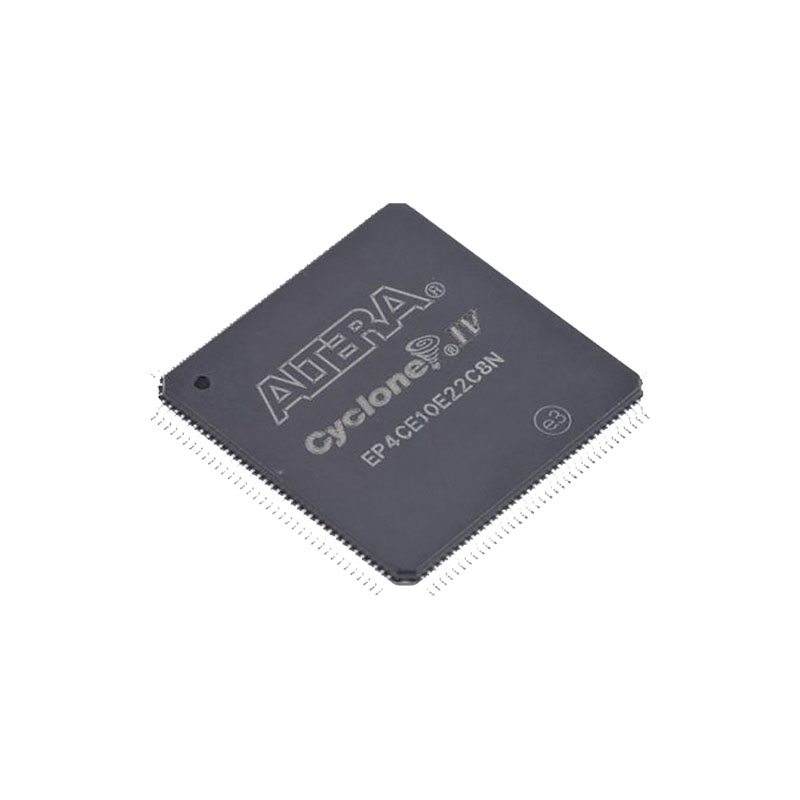

Description:

EP4CE10E22C8N belongs to INTEL/ALTERA’s Cyclone ® IV E FPGA device series. The product series showcases Intel’s leading advantage in providing energy-efficient FPGAs. With enhanced architecture and chips, advanced semiconductor process technology, and power management tools, the power consumption of Cyclone IV FPGA is higher than that of Cyclone ® III FPGA reduces by up to 25%.

Reducing the power consumption of programmable logic devices brings unparalleled advantages to many applications. However, reducing power consumption is only one aspect of system power consumption.

If the technology of reducing power consumption is not adopted, the use of submicron semiconductor technology will significantly increase static power consumption. Due to the increase in leakage current threshold, adopting sub micron process technology will increase static power consumption.

Intel has minimized leakage current and thus reduced static power consumption by adopting low-power (LP) process technology commonly used in handheld components by leading semiconductor manufacturers. This advanced technology reduces physical size and, combined with architecture optimization, can help Cyclone ® IV FPGA minimizes dynamic and static power consumption. Intel in Cyclone ® The IV FPGA adopts multiple process and architecture enhancement techniques, including the use of low dielectric constant materials, variable channel length and oxide layer thickness, and multi transistor threshold voltage.

Applications:

Small applications:

Wireless field

Wired field

Broadcasting field

Industrial sector

Consumer and communication industries, etc

Features:

The cyclical redundancy check (CRC) error detection feature during user mode is supported in all Cyclone IV GX devices. For Cyclone IV E devices, this feature is only supported for the devices with the core voltage of 1.2 V.

■ Cyclone IV E devices are enhanced for lowest power,high functionality with the lowest cost. If your application requires high-speed transceivers up to 3.125 Gbps, choose a GX devicevariant.Otherwise, choose an E variant for high functionality with the lowest cost.

■Cyclone IV E devices are offered incore voltage of 1.0 V and 1.2 V.

■Cyclone IV E devices are available in space-saving Enhanced Thin Quad Flat Pack (EQFP) and FineLine BGA (FBGA) packages with various I/O pin counts.

■Cyclone IV E devices only have GPLLs.

■Cyclone IV E devices provide up to 15 dedicated clock pins (CLK[15..1]) that can drive up to 20 GCLKs. Cyclone IV E devices support three dedicated clock pins on the left side and four dedicated clock pins on the top, right, and bottom sides of the device except EP4CE6 and EP4CE10 devices. EP4CE6 and EP4CE10 devices only support three dedicated clock pins on the left side and four dedicated clock pins on the right side of the device. Check that your chosen device density package combination includes enough PLLs and clock routing resources for your design. GCLK resources are shared between certain PLLs, which can affect which inputs are available for use.

■Cyclone IV E devices are available in four speed grades—6, 7, 8, and 9 (6 is the fastest). Generally, the faster devices cost more.

■AP configuration is only supported in Cyclone IV E devices.FPP configuration is only supported in EP4CGX30 (only for F484 package), EP4CGX50, EP4CGX75, EP4CGX110, EP4CGX150, and all Cyclone IV E devices.

■The Cyclone IV E core voltage VCCINT is 1.2 V or 1.0 V.

■Cyclone IV E devices have eight I/O banks.

■Cyclone IV E devices provide up to 15 dedicated clock pins (CLK[15..1]) that can drive up to 20 GCLKs. Cyclone IV E devices support three dedicated clock pins on the left side and four dedicated clock pins on the top, right, and bottom sides of the device except EP4CE6 and EP4CE10 devices. EP4CE6 and EP4CE10 devices only support three dedicated clock pins on the left side and four dedicated clock pins on the right side of the device.

■Cyclone IV E devices only have GPLLs. The GPLLs are used for general-purpose applications in the FPGA fabric and periphery such as external memory interfaces.

■There are a maximum of 20 clock control blocks available in each Cyclone IV E device.