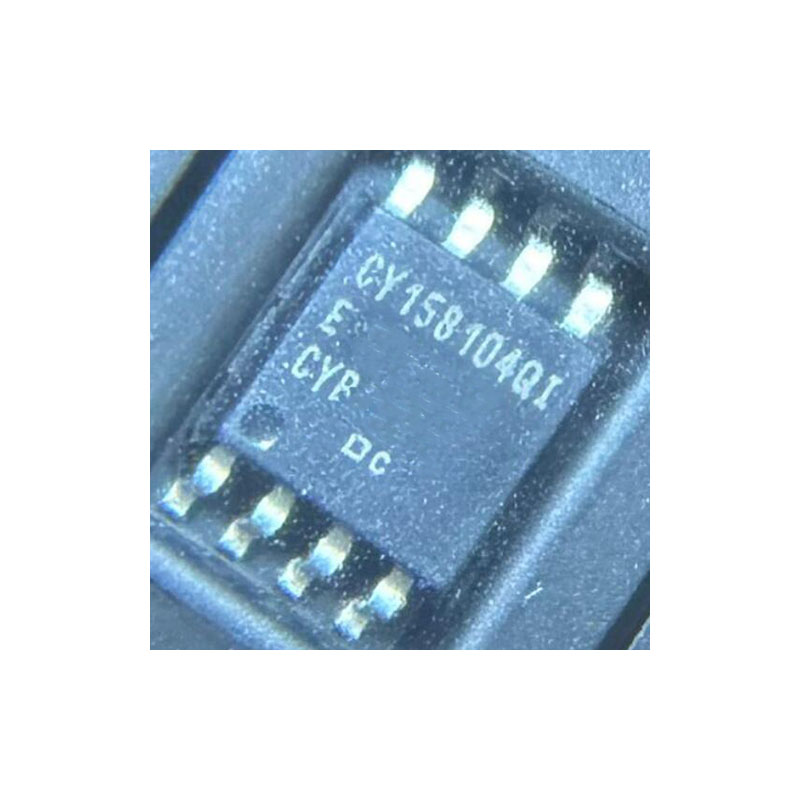

Description:

The CY15B104Q is a 4-Mbit nonvolatile memory employing an advanced ferroelectric process. A ferroelectric random access memory or F-RAM is nonvolatile and performs reads and writes similar to a RAM. It provides reliable data retention for 151 years while eliminating the complexities, overhead, and system-level reliability problems caused by serial flash, EEPROM, and other nonvolatile memories.

Unlike serial flash and EEPROM, the CY15B104Q performs write operations at bus speed. No write delays are incurred. Data is written to the memory array immediately after each byte is successfully transferred to the device. The next bus cycle can commence without the need for data polling. In addition, the product offers substantial write endurance compared to other nonvolatile memories. The CY15B104Q is capable of supporting 1014 read/write cycles, or 100 million times more write cycles than EEPROM.

These capabilities make the CY15B104Q ideal for nonvolatile memory applications, requiring frequent or rapid writes. Examples range from data collection, where the number of write cycles may be critical, to demanding industrial controls where the long write time of serial flash or EEPROM can cause data loss.

The CY15B104Q provides substantial benefits to users of serial EEPROM or flash as a hardware drop-in replacement. The CY15B104Q uses the high-speed SPI bus, which enhances the high-speed write capability of F-RAM technology. The device incorporates a read-only Device ID that allows the host to determine the manufacturer, product density, and product revision. The device specifications are guaranteed over an industrial temperature range of –40 °C to +85 °C.

Features:

4-Mbit ferroelectric random access memory (F-RAM) logicallyorganized as 512 K × 8

High-endurance 100 trillion (1014) read/writes

151-year data retention

NoDelay™ writes

Advanced high-reliability ferroelectric process

Very fast serial peripheral interface (SPI)

Up to 40-MHz frequency

Direct hardware replacement for serial flash and EEPROM

Supports SPI mode 0 (0, 0) and mode 3 (1, 1)

Sophisticated write protection scheme

Hardware protection using the Write Protect (WP) pin

Software protection using Write Disable instruction

Software block protection for 1/4, 1/2, or entire array

Manufacturer ID and Product ID

Low power consumption

300 mA active current at 1 MHz

100 mA (typ) standby current

3 mA (typ) sleep mode current

Low-voltage operation: VDD = 2.0 V to 3.6 V

Industrial temperature: –40 °C to +85 °C

Restriction of hazardous substances (RoHS) compliant

Applications:

Bringing a whole new lifestyle and health experience to today’s connected citizen

Consumer electronics

Space applications

Overview

The CY15B104Q is a serial F-RAM memory. The memory array is logically organized as 524,288 × 8 bits and is accessed using an industry-standard serial peripheral interface (SPI) bus. The functional operation of the F-RAM is similar to serial flash and serial EEPROMs. The major difference between the CY15B104Q and a serial flash or EEPROM with the same pinout is the F-RAM’s superior write performance, high endurance, and low power consumption.

Memory Architecture

When accessing the CY15B104Q, the user addresses 512K locations of eight data bits each. These eight data bits are shifted in or out serially. The addresses are accessed using the SPI protocol, which includes a chip select (to permit multiple devices on the bus), an opcode, and a three-byte address. The upper 5 bits of the address range are ‘don’t care’ values. The complete address of 19 bits specifies each byte address uniquely. Most functions of the CY15B104Q are either controlled by the SPI interface or handled by on-board circuitry. The access time for the memory operation is essentially zero, beyond the time needed for the serial protocol. That is, the memory is read or written at the speed of the SPI bus. Unlike a serial flash or EEPROM, it is not necessary to poll the device for a ready condition because writes occur at bus speed. By the time a new bus transaction can be shifted into the device, a write operation is complete. This is explained in more detail in the interface section.